# A Multiple Window Demonstration of the Operation of PN Diodes Using DEVSIM\*

D. DONOVAL and J. RACKO

Microelectronics Department, Slovak Technical University, Bratislava, Slovakia

G. WACHUTKA and H. BALTES

Physical Electronics Laboratory, Swiss Federal Institute of Technology, Zurich, Switzerland

The one-dimensional device simulator DEVSIM is a useful tool for the multiple window demonstration of the operation of forward- and reverse-biased PN diodes. The graphical user interface allows for correlating the output I-V and C-V characteristics with internal device properties such as the spatial distributions of the electric potential, the electric field, the free carriers, their mobility and velocity, the band gap diagram and other quantities which are not ready for direct measurement. In combination with process simulation, the influence of variations in the technological process conditions on the output electrical characteristics can be analysed.

## 1. INTRODUCTION

MODELLING and numerical simulation play an increasingly important role in the development of modern technologies. By means of simulation, microscopic physical phenomena and effects occurring on very small length scales and on very short time scales can be visualised in macroscopic dimensions and, thus, made perceivable to our eyes and mind. Highly sophisticated physical models are implemented in the simulation tools, providing realistic results with good agreement between the real and the virtual (simulated) world. Hence, simulation is useful not only for qualitative understanding, but even for the quantitative predictive analysis of the properties of new semiconductor structures and devices.

Physical electronics is a typical example where modelling and simulation have proved to be very powerful and effective tools for research and development, including their use for education and training. Here, the calculation of electrical quantities and characteristics of semiconductor structures implies the numerical solution of the basic semiconductor equations, i.e. the coupled set of Poisson equations, the continuity equations for carrier flow and the constitutive current relations (drift-diffusion equations). Physical models, which include the dependence on temperature, doping concentration and electric field, are implemented in the numerical solution procedures. There exist various two- and three-dimensional simulators such as PISCES and DAVINCI distributed by American vendors, SIMUL developed at the Swiss

Federal Institute of Technology Zurich, and MINIMOS and BAMBI developed by the Technical University Vienna, which feature highly advanced models and are applicable even to very complex device structures. However, the visualisation and interpretation of the simulated results are non-trivial problems and require much expertise from the user. Therefore, there is still a need for a reliable one-dimensional simulator with a flexible and user-friendly graphical support, in particular with a view to training and educational purposes.

# 2. DESCRIPTION OF OUR DEVICE SIMULATOR

Running the device simulator DEVSIM [1] requires an AT-compatible PC (e.g. with 386 + 387 or 486 processor) operated under the Windows surface, thereby providing a flexible and easy-to-use graphical environment [2]. The program code is written in Turbo Pascal and has a modular architecture. Therefore, new and more complex physical models may easily be added to the program or substituted for the old ones.

On parallel-opened windows, several quantities are simultaneously displayed, thus allowing the immediate correlation of the electrical characteristics with internal quantities such as doping profile and other structural properties. Internal dynamic variables within the structure considered as, for example, the electrostatic potential and the electric field, the distributions of the free carriers, their mobilities and velocities, and other physical properties which are not ready for direct measurement, are simultaneously visualised on the screen. So simulation leads to unique insight into the internal semiconductor structures. DEVSIM is based on

<sup>\*©</sup> DEVSIM is a trademark of Microelectronics Department, Slovak Technical University, Bratislava, Slovakia.

advanced physical models [3, 4] where the physical parameters may be adjusted by the user in order to validate the models for a given technological process. Emphasis is laid on a judicious treatment of metal-semiconductor junctions. So, for instance, a special boundary condition for Schottky contact

[5] is implemented.

DEVSIM is very easy to use. An integrated online help function facilitates the operation of the simulator so that virtually anybody with a basic knowledge of personal computers will be familiar with the simulator after a short time. The impact of the DEVSIM on user knowledge is even stronger when it is used together with some one-dimensional process simulator which provide a doping profile of active impurities in the formatted data file (dimension in the first column, net doping in the second and total concentration of impurities in the third). The influence of technological data which characterise the device fabrication on the electrical output characteristics can be analysed.

#### 3. EXAMPLE

The examples discussed in the figures illustrate the performance of DEVSIM and elucidate its advantages in training students in the field of

physical electronics.

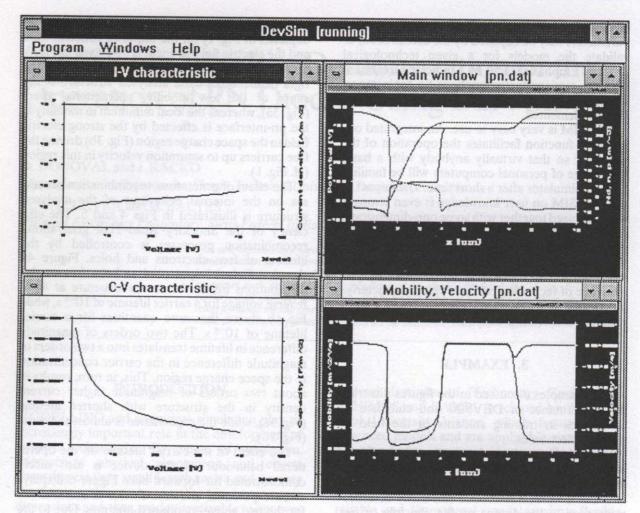

Figure 1 shows a typical example of the multiplewindow visualisation of simulated results using the Windows surface. The calculated output electrical I-V and C-V characteristics can easily be crossreferenced to the doping profile, the free carrier concentration and the mobility and drift velocity of the free carriers in the interior of the device structure under analysis.

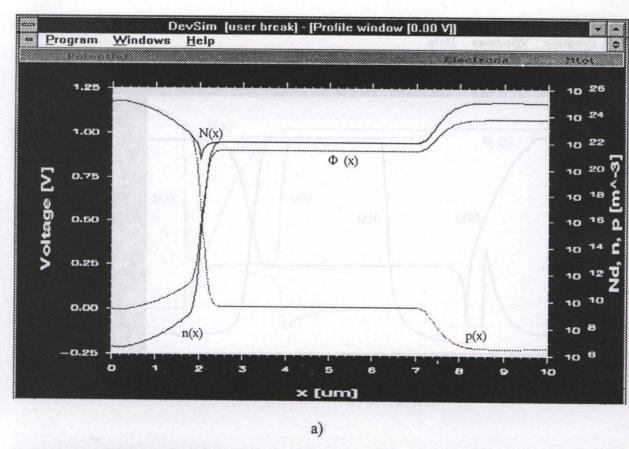

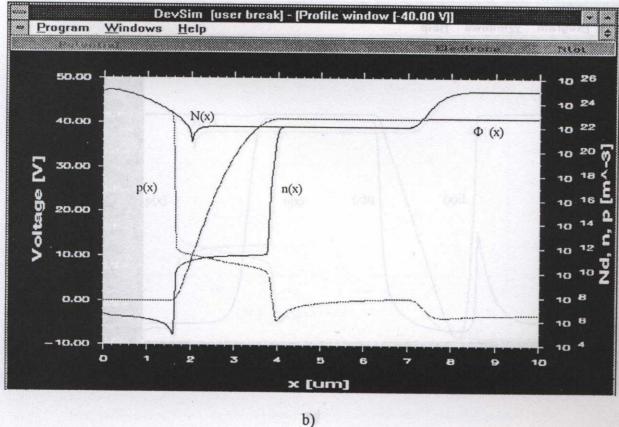

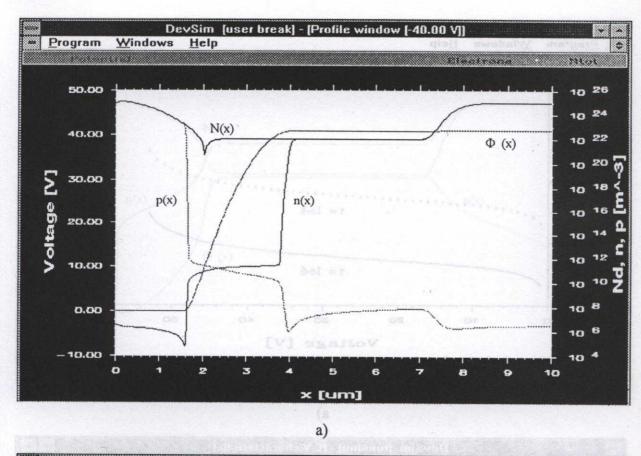

Let us first consider the case of a reverse biased pn-junction. We assume an epitaxial layer of n-type Si with a donor concentration  $N_d = 10^{16}$ , cm<sup>-3</sup>, grown on a high conductivity substrate with  $N_d$  = 1019 cm<sup>-3</sup>. An abrupt pn-junction is formed by a boron diffusion with a surface concentration of  $N_a$ =  $10^{19}$  cm<sup>-3</sup>. The lifetime of the free electrons and

holes is set to  $\tau_{\rm n,p} = 10^{-6} \, {\rm s}^{-1}$ . Figure 2 shows the distribution of free carriers, net doping profile and electrostatic potential distribution in the equilibrium state (a) and in the state biased by the applied voltage (b). The value of built-in voltage as well as the thickness of a space charge region around the pn-junction can be determined. The changes in the thickness of the space charge region and in the free carrier concentrations due to the variation of the applied voltage may directly be correlated with the output I-V and C-V characteristic (Fig. 1). Also the influence of the doping profile on current density and capacitance can easily be analysed. To this end, it is advantageous to use the device simulator in combination with a suitable process simulator which generates the doping profile for the different technological process parameters used during sample preparation.

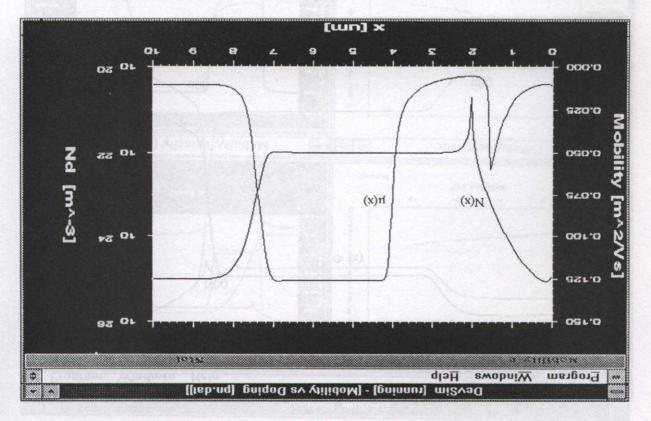

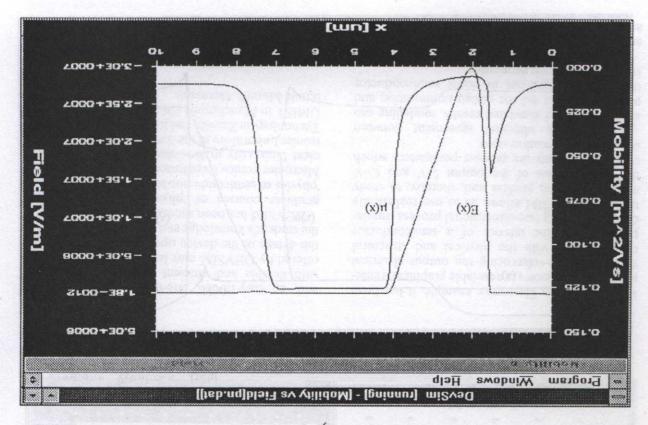

The dependence of the carrier mobility (as depicted in Fig. 1) on the impurity concentration and the electric field strength is displayed in Fig. 3. The high concentration of impurities at the left- and right-hand ends of the analysed structure is the cause of the low mobility encountered there (Fig. 3a), whereas the local minimum in mobility at the pn-interface is effected by the strong electric field in the space charge region (Fig. 3b) driving the free carriers up to saturation velocity in this region

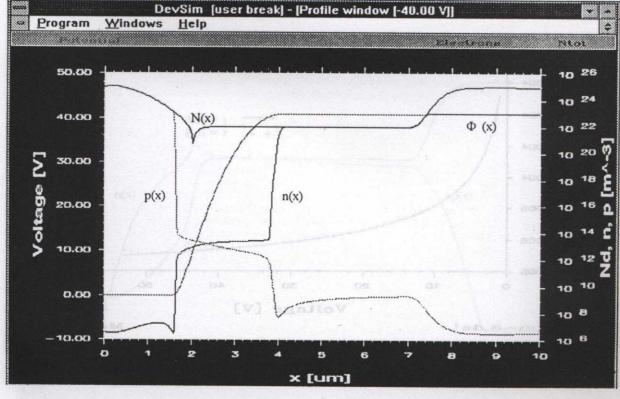

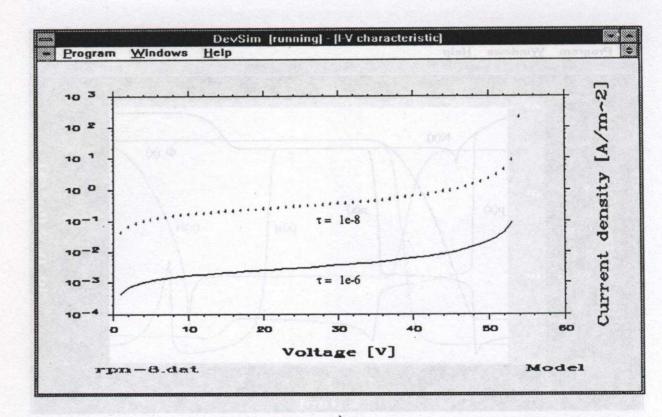

The effect of generation-recombination processes on the internal behaviour of the analysed structure is illustrated in Figs 4 and 5. The efficiency of the Shockley-Read-Hall generationrecombination processes is controlled by the lifetime of free electrons and holes. Figure 4a shows the electric potential and the free-carrier distributions inside the device structure at 40 V reverse voltage for a carrier lifetime of 10-6 s, while Fig. 4b shows the same quantities for a carrier lifetime of 10-8 s. The two orders of magnitude difference in lifetime translates into a two orders of magnitude difference in the carrier concentration in the space charge region. This, in turn, results in about two orders of magnitude higher current density in the structure with shorter lifetime (Fig. 5a), while the capacitance is almost the same (Fig. 5b).

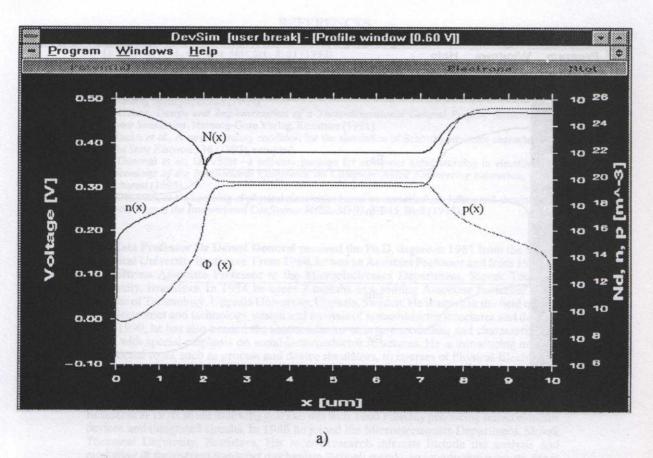

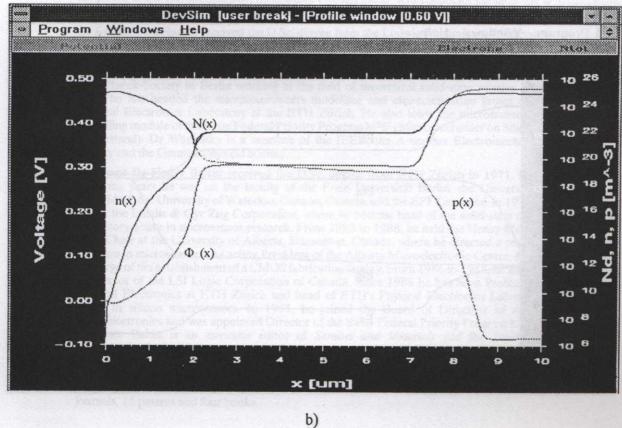

The effect of the carrier lifetime on the operational behaviour of the device is also nicely demonstrated for forward bias. Figure 6 displays electric potential and free-carrier concentrations for the two above-mentioned lifetimes. Due to the higher recombination rate at the shorter lifetime, the diffusion length of the free carriers is lower for the diode with a lifetime of  $10^{-8}$  s (Fig. 6b). This results in a significantly stronger decay of the minority carrier concentration at each side of the pn-junction when compared to the structure with a

carrier lifetime of  $10^{-6}$  s (Fig. 6a).

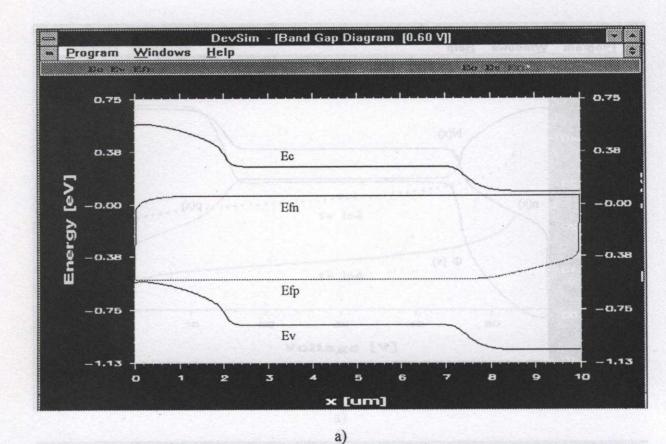

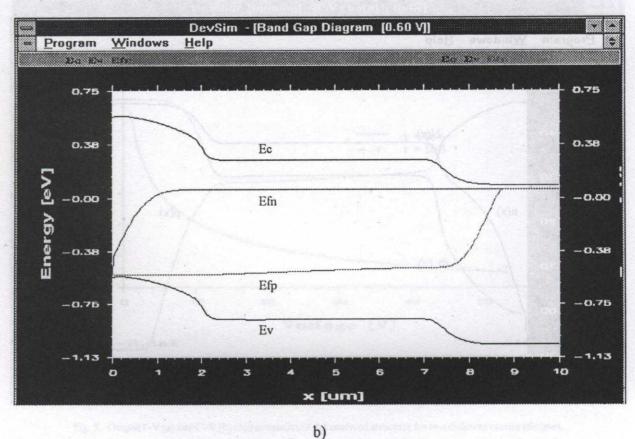

The energy band diagram and the splitting of the quasi-Fermi level in the forward-biased case are shown in Fig. 7. Again the influence of varying diffusion length caused by different lifetimes of the free carriers is clearly visible. For the shorter carrier lifetime, the diffusion length is shorter and, hence, the quasi-Fermi levels coincide over a considerable distance on the right-hand part of the diode (Fig 7b), while in the structure with the longer carrier lifetime the quasi-Fermi levels are different everywhere except for the contacts at the right- and left-hand boundaries, where they become equal in consequence of the boundary conditions imposed (Fig. 7a).

### 4. CONCLUSION

We have demonstrated the advantage of 'multiple-window display' or simulation results in the analysis of semiconductor devices, in particular with a view to educational purposes. With a

Fig. 1. Multiple-window display of simulation results computed by DEVSIM.

PIN diode as an illustrative example, it has been shown that Windows is a suitable graphical framework for cross-referencing the output electrical characteristics with the physical and structural properties in the interior of a semiconductor device. Coupling one-dimensional process simulation with DEVSIM allows us to use realistically modelled doping profiles and, thereby, to study the dependencies of the output I–V and C–V characteristics on the process parameters which control the fabrication steps.

After having obtained agreement between experiments and simulated results, modelling can provide valuable aid for design optimisation and the predictive analysis of novel semiconductor structures and their properties.

Furthermore, device simulation has proven to be an increasingly helpful technique in the education and training of microelectronics students. To this end, an easy-to-use, one-dimensional simulator with flexible and efficient graphical support as offered by DEVSIM may lend unique insight into the details of the device operation, thus enlarging the student's knowledge and expertise [6, 7].

DEVSIM has been successfully employed in the graduate courses of 'physical electronics' and 'physics of semiconductor structures' taught at the Microelectronics Department of the Slovak Technical University in Bratislava, the Physical Electronics Laboratory of the Swiss Federal Institute of Technology in Zurich, and it is also implemented at UMIST in Manchester, UK and at the Fachhochschule Munich, Germany.

Acknowledgement—The authors would like to express their gratitude to Professor M. S. Wald of the Hamburg Educational Partnership, Hamburg, Germany, for contributing supplementary ideas during the preparation of this manuscript.

Fig. 2. Free-carrier distributions, doping profile and distribution of electrostatic potential in thermal equilibrium (a) and at reverse voltage of  $V_r = 40 \text{ V}$  (b).

(8

Fig. 3. Dependence of the carrier mobility on net doping concentration (a) and on the electric field strength (b).

(9

Fig. 4. Distribution of electric potential and free-carrier concentration in the interior of the analysed structure at  $V_{\tau} = 40 \text{ V}$  for  $\tau = 10^{-6} \text{ s}$  (a) and  $\tau = 10^{-8} \text{ s}$  (b).

b)

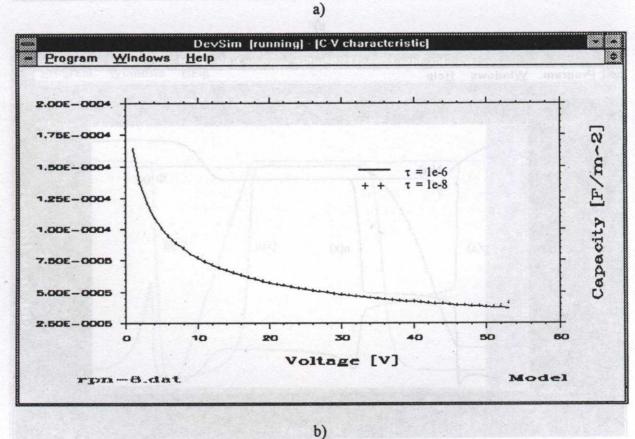

Fig. 5. Output I-V (a) and C-V (b) characteristics of the analysed structure for two different carrier lifetimes.

Fig. 6. Distribution of electric potential and free carrier concentration in the interior of the analysed structure at  $V_i = 0.40$  V for  $\tau = 10^{-6}$  s (a) and  $\tau = 10^{-8}$  s (b).

Fig. 7. Energy band diagram of the analysed structure at  $V_f = 0.40 \text{ V}$  for  $\tau = 10^{-6} \text{ s}$  (a) and  $\tau = 10^{-8} \text{ s}$  (b).

#### REFERENCES

1. D. Donoval et al., Comput. Mat. Sci., 1, 51 (1992).

J. Hromcova et al., The role of graphical user environment in the analysis of properties of semiconductor structure, presented at CAE-SQA '93, 14-16 May 1993, Szklarska Poreba, Poland.

S. Selberherr, Physical models for silicon VLSI, in Ch. M. Snowden (ed.), Semiconductor Device Modelling Springer, Berlin (1989).

G. Heiser, Design and Implementation of a Three-dimensional General Purpose Semiconductor Device Simulation, Hartung-Gore Verlag, Konstanz (1991).

J. Racko et al., A new boundary condition for the simulation of Schottky structure characteristics, Solid State Electron., 36 (1993), accepted.

D. Donoval et al., DEVSIM—a software package for computer aided learning in electronics, in Proceedings of the International Conference on Computer Aided Engineering Education, p. 413, Bucharest (1993).

D. Donovan, et al., Learning of physical electronics based on numerical modelling and simulation, in Proceedings of the International Conference MIEL-SD 93, p. 345, Bled (1993).

Associate Professor Dr Daniel Donoval received the Ph.D. degree in 1981 from the Slovak Technical University Bratislava. From 1980, he was an Assistant Professor and from 1987, he has been an Associate Professor at the Microelectronics Department, Slovak Technical University, Bratislava. In 1984 he spent 3 months as a visiting Associate Professor at the Institute of Technology, Uppsala University, Uppsala, Sweden. He is active in the field of physical electronics and technology, design and analysis of semiconductor structures and devices. Since 1990, he has also headed the semiconductor structure modelling and characterization group with special emphasis on metal-semiconductor structures. He is introducing modern educational tools, such as process and device simulators, to courses of Physical Electronics, Technology of Integrated Circuits and related topics. Dr Donoval is a member of the Slovak Electrotechnical Society and Slovak Physical Society.

**Juraj Racko** graduated in electrical engineering from the Slovak Technical University, Bratislava in 1976. In the following years he was with Tesla Piestany producing semiconductor devices and integrated circuits. In 1986 he joined the Microelectronics Department, Slovak Technical University, Bratislava. His recent research interests include the analysis and modelling of the current transport mechanism through metal–semiconductor contacts. He is also active in microsensor and micromechanics technology.

Dr Gerhard Wachutka received the D.Sc. degree from the Ludwig-Maximilians-Universität Munich in 1985. From 1985 to 1988, he was with Siemens Corporate Research & Development, Munich, where he headed a modelling group active in the development of modern high-power semiconductor devices. In 1989, he joined the Fritz-Haber Institute of the Max-Planck-Society in Berlin working in the field of theoretical solid-state physics. Since 1990 he has headed the microtransducers modelling and characterisation group of the Physical Electronics Laboratory at the ETH Zürich. He also leads the microtransducers modelling module of the Swiss Federal Priority Program M<sup>2</sup>S<sup>2</sup> (Micromechanics on Silicon in Switzerland). Dr Wachutka is a member of the IEEE, the American Electromechanical Society and the German Physical Society.

Professor Dr Henry Baltes received the D.Sc. degree from ETH Zürich in 1971. In the following years he was on the faculty of the Freie Universität Berlin, the University of Düsseldorf, the University of Waterloo, Ontario, Canada, and the EPF Lausanne. In 1974, he joined the Landis & Gyr Zug Corporation, where he became head of the solid-state device laboratory active in microsensor research. From 1983 to 1988, he held the Henry Marshall Tory Chair at the University of Alberta, Edmonton, Canada, where he directed a research program in microsensors. As acting President of the Alberta Microelectronic Centre, he was in charge of the establishment of a CMOS fabrication facility. From 1986 to 1988, he was also a Director of the LSI Logic Corporation of Canada. Since 1988 he has been Professor of Physical Electronics at ETH Zürich and head of ETH's Physical Electronics Laboratory active in silicon microsensors. In 1991, he joined the Board of Directors of Ascom Microelectronics and was appointed Director of the Swiss Federal Priority Program LESIT. Professor Baltes is an associate editor of Sensors and Materials and the Journal of Micromechanics and Microengineering. He is a member of the IEEE, the Optical Society of America, the Electromechanical Society, the Swiss Information Technology Society, the Swiss Electrotechnical Association, the Swiss Society for Sensor Technology and the Swiss Physical Society. He has authored or co-authored over 250 publications in scientific or technical journals, 15 patents and four books.